Pin grid array

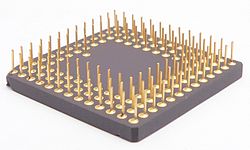

La matriz de rejilla de pines[1][2] o PGA (del inglés pin grid array) es una interfaz de conexión a nivel físico para microprocesadores y circuitos integrados o microchips.

También se denomina de la misma forma a la cápsula o empaquetado de los circuitos integrados (IC). Su alineación de pines se presenta en forma vertical y horizontal.

Originalmente PGA es el zócalo clásico para la inserción en una placa base de un microprocesador. Fue usado para procesadores como: Intel 80386 e Intel 80486.

Visión general

editarEl zócalo de CPU consiste en un cuadrado de conectores en forma de agujero donde se insertan los pines del chip por medio de presión. Según el tipo de chip, tendrá más o menos agujeros (uno por cada patilla).1956

Encapsulado o empaquetado

editarEn un PGA, el IC se monta en una losa de cerámica, que presenta una matriz de contactos o olas en una de sus caras. Luego, los pines se pueden insertar en los agujeros de un circuito impreso y soldarse.

Casi siempre se espacian 2.54 milímetros entre sí. Para un número dado de pines, este tipo de paquete ocupa menos espacio que los tipos más viejos como el dual in-line package (DIP o DIL).

Variantes del PGA

editarLas versiones plastic pin grid array (PPGA) y posteriormente flip-chip pin grid array (FCPGA), fueron creadas por Intel Corporation para los microprocesadores Intel Pentium, y a menudo son usados en placas base con zócalos de CPU ZIF (zero insertion force) para proteger los delicados pines.

Lista de zócalos PGA

editarVéase también

editarReferencias

editar- ↑ Services, ProZ.com Translation. «PGA > (Pin Grid Array). Matriz de reja de pines». www.proz.com. Consultado el 17 de octubre de 2016.

- ↑ «1.1.2.2. CPU». cisco.uttecamac.edu.mx. Consultado el 17 de octubre de 2016.

Enlaces externos

editar- Wikimedia Commons alberga una categoría multimedia sobre Pin grid array.

- Socket FM2 (en inglés).

- Socket FM2+ (en inglés).